# **Contents GPIO Interface**

- Chapter 1 <u>Overview and Configuration</u>

- Chapter 2 Interface Description

- Chapter 3 <u>HTBasic Software Interface</u>

- Chapter 4 Programming Guide for GPIO 600

- Chapter 5 Programming Guide for GPIO 650

Copyright ® 1988-2001 by TransEra Corp.

{button www.htbasic.com,Inet("www.htbasic.com")}

# **Chapter 1 Overview and Configuration**

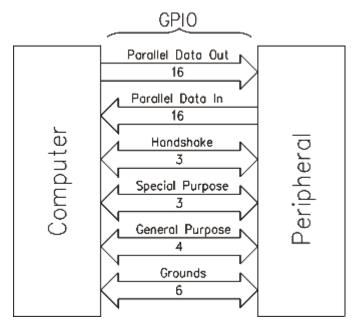

The function of the General Purpose Input Output (GPIO) interface is to provide a means of communication between a peripheral device and a computer.

### **Block Diagram of the GPIO Interface**

The GPIO interface uses a 50 pin connector to communicate with the peripheral. Thirty-two lines are used for data input and output; sixteen for output (DO0 - DO15) and sixteen for input (DI0 - DI15).

Three lines are used for handshaking purposes. They are the Peripheral Control line (PCTL), Peripheral Flag line (PFLG), and Input/Output line (IO).

The three Special Purpose lines are External Interrupt Request (EIR), Peripheral Status (PSTS), and Peripheral Reset (PRESET).

The four General Purpose lines are CTL0, CTL1, STI0, and STI1.

Six ground lines are provided for a ground reference and safety.

The last two lines are not connected.

Throughout this manual an output refers to a transfer of data from the computer to the peripheral while an input is a transfer from the peripheral to the computer. This notation applies to the data bus and the signal lines.

This manual has information to configure both the GPIO 650 and the GPIO 600.

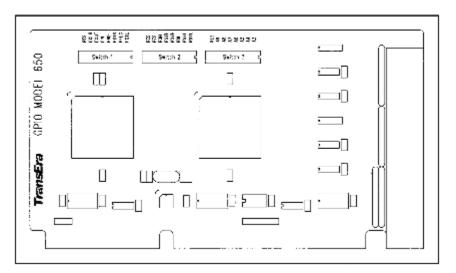

# **GPIO 650 Hardware Setup**

The GPIO 650 board has three switches that are used to configure the board. An understanding of the GPIO interface is necessary to properly set the switches. If you have not previously used the GPIO interface please study the Interface Description section before proceeding with the installation.

Switches labeled RES are reserved and currently unused. The switch is ON when it is toward the PC board and OFF when it is away from the board.

#### Location of Switches for the GPIO 650

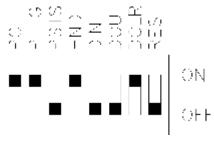

GPIO 650 Switch 1

# **GPIO 650 Switch One - Interface Settings**

This switch selects the signal polarity, type of handshaking and the state of the output data lines after reset. The table shows the effect of each switch setting.

| Name of<br>Switch<br>Position | PCTL                       | PFLG                       | PSTS                       | HND                     | DIN                           | DOUT                           | DCLR                   |

|-------------------------------|----------------------------|----------------------------|----------------------------|-------------------------|-------------------------------|--------------------------------|------------------------|

| Function                      | Set<br>Polarity of<br>PCTL | Set<br>Polarity of<br>PFLG | Set<br>Polarity of<br>PSTS | Full/Pulse<br>Handshake | Set<br>Polarity of<br>Data In | Set<br>Polarity of Data<br>Out | Clear DOUT on<br>Reset |

| ON                            | Low = Set                  | Low = Rdy                  | Low = OK                   | Full                    | Low = 1                       | Low = 1                        | Yes                    |

|                               | High = Clr                 | High = Bsy                 | High = OK                  |                         | High = 0                      | High = 0                       |                        |

| OFF                           | Low = Clr                  | Low = Bsy                  | Low = OK                   | Pulse                   | Low = 0                       | Low = 0                        | No                     |

|                               | High = Set                 | High = Rdy                 | High = OK                  |                         | High = 1                      | High = 1                       |                        |

#### **Interface Settings for GPIO 650**

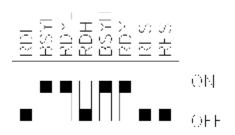

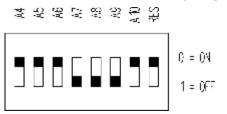

### GPIO 650 Switch 2

### **GPIO 650 Switch Two - Input Clock Source**

Switch two selects the latch source that will clock the data into the input data buffers. The switch for the **desired clock should be off** with the other two on. The clocks for the high and low bytes do not need to be the same.

The RD clock source causes the computer to clock the input buffers whenever it is reading the data. The BSY clock source causes the input buffers to be loaded on the ready-to-busy transition of PFLG. The RDY clock source uses the busy-to-ready transition of PFLG.

By default these settings select the input clock source. Software can override these settings. If only software control is used for the input clock source selection this switch does not need to be set.

For more information on GPIO input clocking, refer to the Interface Description section for a more detailed explanation.

### GPIO 650 Switch 3 GPIO 650 Switch Three - I/O Address

This switch is used to select the I/O address of the board. The I/O address is the base address that the computer uses to communicate with the board. The GPIO 650 board uses 8 address locations above and including the base address. The address space of the GPIO board cannot be shared with any other peripheral. The default address of the GPIO board is 380h.

The following table shows the switch settings with the corresponding hexadecimal board address.

| Address Selection for GPIO 650 |             |          |             |  |  |  |

|--------------------------------|-------------|----------|-------------|--|--|--|

| Switches                       | I/O Address | Switches | I/O Address |  |  |  |

| A9<br>A3                       | (hex)       | A9<br>A3 | (hex)       |  |  |  |

| 1000000                        | 200         | 1100000  | 300         |  |  |  |

| 1000001                        | 208         | 1100001  | 308         |  |  |  |

| 1000010                        | 210         | 1100010  | 310         |  |  |  |

| 1000011                        | 218         | 1100011  | 318         |  |  |  |

| 1000100                        | 220         | 1100100  | 320         |  |  |  |

#### . . . ...

| 1000101 | 228   | 1100101 | 328   |

|---------|-------|---------|-------|

| 1000110 | 230   | 1100110 | 330   |

| 1000111 | 238   | 1100111 | 338   |

| 1001000 | 240   | 1101000 | 340   |

| 1001001 | 248   | 1101001 | 348   |

| 1001010 | 250   | 1101010 | 350   |

| 1001011 | 258   | 1101011 | 358   |

| 1001100 | 260   | 1101100 | 360   |

| 1001101 | 268   | 1101101 | 368   |

| 1001110 | 270   | 1101110 | 370   |

| 1001111 | 278   | 1101111 | 378   |

| 1010000 | 280   | 1110000 | 380   |

| 1010001 | 288   | 1110001 | 388   |

| 1010010 | 290   | 1110010 | 390   |

| 1010011 | 298   | 1110011 | 398   |

| 1010100 | 2 A 0 | 1110100 | 3 A 0 |

| 1010101 | 2 A 8 | 1110101 | 3 A 8 |

| 1010110 | 2 B 0 | 1110110 | 3 B 0 |

| 1010111 | 2 B 8 | 1110111 | 3 B 8 |

| 1011000 | 2 C 0 | 1111000 | 3 C 0 |

| 1011001 | 2 C 8 | 1111001 | 3 C 8 |

| 1011010 | 2 D 0 | 1111010 | 3 D 0 |

| 1011011 | 2 D 8 | 1111011 | 3 D 8 |

| 1011100 | 2 E 0 | 1111100 | 3 E 0 |

| 1011101 | 2 E 8 | 1111101 | 3 E 8 |

| 1011110 | 2 F 0 | 1111110 | 3 F 0 |

| 1011111 | 2 F 8 | 1111111 | 3 F 8 |

|         |       |         |       |

### **GPIO 650 Interrupt and DMA Channels**

Interrupts and DMA are used to assist the transferring of data. There are a fixed number of interrupt and DMA channels on a PC and they cannot be shared with other devices. The GPIO 650 enables the channel(s) for use with software so no hardware settings are required.

Interrupt Channels 5, 7, 9, 10, 11, 12, 15

DMA Channels 5, 6, 7

The board can use one interrupt channel and one DMA channel. An interrupt must be selected for DMA to be used. These channels numbers are given to the software driver during the initialization procedure. If there are no interrupt or DMA channels allocated to the board it can still be used to transfer data but it's performance will decrease and interrupts will not be available.

The three DMA channels are the 16-bit DMA channels available on a PC. These channels do not support 8-bit transfers. To handle this limitation the GPIO 650 was designed to pack two 8-bit peripheral handshakes into a single DMA transfer. This not only allows 8-bit peripheral

transfers but also doubles the effective 8-bit transfer rate of the GPIO board.

More detailed information on DMA transfers is in Interface Description under DMA Transfers.

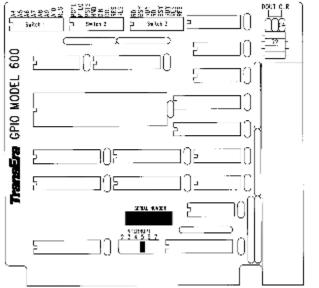

# **GPIO 600 Hardware Setup**

The GPIO 600 board has three switches that are set to configure the board. An understanding of the GPIO interface is necessary to properly set the switches. If you have not previously used the GPIO interface please study the *Interface Description* section before proceeding with the installation.

Switches labeled RES are reserved. The switch is ON when it is toward the PC board and OFF when it is away from the board.

Location of Switches and Jumpers on the GPIO 600

### GPIO 600 Switch 1 GPIO 600 Switch One - I/O Address

This switch is used to select the I/O address of the board. The I/O address selected by this switch is the base address that the computer uses to communicate with the board. The GPIO board uses 16 address locations above the base address. The address space of the GPIO board cannot be used by any other peripheral. The default address of the GPIO board is 380h.

The following table shows the switch settings with the corresponding hexadecimal board address.

#### Address Selection for GPIO 600

| Switches  | I/O Address |

|-----------|-------------|

| A10<br>A4 | (hex)       |

| 0100000 | 200   |

|---------|-------|

| 010001  | 210   |

| 0100010 | 220   |

| 0100011 | 230   |

| 0100100 | 240   |

| 0100101 | 250   |

| 0100110 | 260   |

| 0100111 | 270   |

| 0101000 | 280   |

| 0101001 | 290   |

| 0101010 | 2 A 0 |

| 0101011 | 2 B 0 |

| 0101100 | 2 C 0 |

| 0101101 | 2 D 0 |

| 0101110 | 2 E 0 |

| 0101111 | 2 F 0 |

| 0110000 | 300   |

| 0110001 | 310   |

| 0110010 | 320   |

| 0110011 | 330   |

| 0110100 | 340   |

| 0110101 | 350   |

| 0110110 | 360   |

| 0110111 | 370   |

| 0111000 | 380   |

| 0111001 | 390   |

| 0111010 | 3 A 0 |

| 0111011 | 3 B 0 |

| 0111100 | 3 C 0 |

| 0111101 | 3 D 0 |

| 0111110 | 3 E 0 |

| 0111111 | 3 F 0 |

|         |       |

#### PCTL PFLC PSTS PSTS PSTS PSTS PSTS PSTS RES

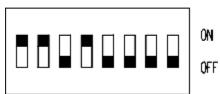

#### GPIO 600 Switch 2

### GPIO 600 Switch Two - Interface Settings This switch selects the signal polarity and the type of handshaking that will be used. The chart below shows the switch settings for handshaking and polarity.

Interface Settings for GPIO 600

|                               |                            |                            |                            | <b>J</b>                |                               |                                |          |

|-------------------------------|----------------------------|----------------------------|----------------------------|-------------------------|-------------------------------|--------------------------------|----------|

| Name of<br>Switch<br>Position | PCTL                       | PFLG                       | PSTS                       | HND                     | DIN                           | DOUT                           | RES      |

| Function                      | Set<br>Polarity of<br>PCTL | Set<br>Polarity of<br>PFLG | Set<br>Polarity of<br>PSTS | Full/Pulse<br>Handshake | Set<br>Polarity of<br>Data In | Set<br>Polarity of Data<br>Out | Reserved |

| ON                            | Low = Set                  | Low = Rdy                  | Low = OK                   | Full                    | Low = 1                       | Low = 1                        |          |

|                               | High = Clr                 | High = Bsy                 | High = OK                  |                         | High = 0                      | High = 0                       |          |

| OFF                           | Low = Clr                  | Low = Bsy                  | Low = OK                   | Pulse                   | Low = 0                       | Low = 0                        |          |

|                               | High = Set                 | High = Rdy                 | High = OK                  |                         | High = 1                      | High = 1                       |          |

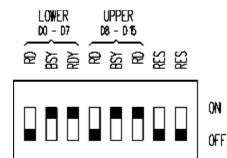

### GPIO 600 Switch 3

### **GPIO 600 Switch Three - Input Clock Source**

This switch selects the latch source that will clock the data into the input data buffers. The switch for the desired clock should be off with the other two on. The clocks for the high and low bytes do not need to be the same.

The RD clock source causes the computer to clock the input buffers whenever it is reading the data. The BSY clock source causes the input buffers to be loaded on the ready-to-busy transition of PFLG. The RDY clock source uses the busy-to-ready transition of PFLG.

For more information on GPIO input clocking, refer to the Interface Description section for a more detailed explanation.

### **Interrupt Jumper**

The GPIO 600 supports interrupts 2 through 7. The default interrupt is 5. The location of the interrupt selector pins can be found on the board diagram at the start of this section. Install the shorting block on the pins that corresponds to the desired interrupt number.

### **DOUT Clear Jumper**

If the DOUT Clear jumper is set, the output data lines will be set low after a board reset. The location of the DOUT Clear jumper can be seen on the board diagram at the start of this section.

# **Board Installation**

- **1.** Turn off and unplug the computer

- 2. Remove the computer cover.

- 3. Locate an empty slot and take off the slot cover by removing the screw. Keep the screw.

- **4.** Eliminate any static electricity by touching the metal computer case.

- 5. Remove the GPIO board from the static protection pouch and insert it into the selected

- slot. The board should be handled by its edges only. **6.** Replace the screw to hold the board in place.

- **7.** Replace the computer cover.

# **Chapter 2 Interface Description**

This chapter describes the operation of the GPIO interface.

| 1        | / -                                  |      |        |

|----------|--------------------------------------|------|--------|

|          |                                      | ~    |        |

| N/C -    | 1                                    | 26 } | - GND  |

| D015 -   | 2                                    | 27   | - DI15 |

| DO14 -   | 3                                    | 28   | - DI14 |

| D013 -   | 4                                    | 29   | - DI13 |

| DO12 -   | 5                                    | 30   | - DI12 |

| DO11-    | 2<br>3<br>4<br>5<br>6<br>7<br>8<br>9 | 31   | - DI11 |

| DO10 -   | 7                                    | 32   | - DI10 |

| DO9 -    | 8                                    | 33   | - DI9  |

| D08 -    | 9                                    | 34   | - DI8  |

| D07 -    | 10                                   | 35   | - DI7  |

| DO6 -    | 11                                   | 36   | - DI6  |

| DO5 -    | 12                                   | 37   | - DI5  |

| DO4 -    | 13                                   | 38   | - DI4  |

| D03 -    | 14                                   | 39   | - DI3  |

| DO2 -    | 14<br>15                             | 40   | - DI2  |

| DO1-     | 16                                   | 41   | - DI1  |

| DO0 -    | 17                                   | 42   | - DIO  |

| GND -    | 18                                   | 43   | - GND  |

| PCTL -   | 19                                   | 44   | - PFLG |

| 1/0 -    | 20                                   | 45   | - PSTS |

| PRESET - | 21                                   | 46   | - EIR  |

| CLTO -   | 22                                   | 47   | - STI0 |

| CTL1 -   | 23                                   | 48   | - STI1 |

| GND -    | 24                                   | 49   | - GND  |

| CHGND -  | 25                                   | 50   | - N/C  |

|          |                                      |      |        |

| ,        |                                      |      |        |

# External Connections to GPIO Signal Descriptions

All of the signal lines of the GPIO board are described below. The numbers in parentheses are the pin numbers on the connector.

### **Parallel Data Out**

Data Output Lines (2-17) - These are the sixteen data output lines. The computer writes to these lines while the peripheral reads them. The logic sense of these lines is user configurable.

### Parallel Data In

Data Input Lines (27-42) - These are the sixteen data input lines. The peripheral writes to these lines while the computer reads them. The logic sense of these lines is user configurable.

### Handshake

Peripheral Control (19) - PCTL - This is the control line that the computer sets to initiate a transfer of data. The logic sense of this line is user configurable.

Input Output (20) - IO - This line indicates the direction of data flow to the peripheral. A high signal indicates an input while a low signal indicates an output.

Peripheral Flag (44) - PFLG - The peripheral uses this line to acknowledge the transfer. The logic sense of this line is user configurable.

### **Special Purpose**

Peripheral Status (45) - PSTS - This line can be used to indicate the OK or not OK status of the peripheral. The logic sense of this line is user configurable.

Peripheral Reset (21) - PRESET - This is the reset line. It pulses low for at least 15 microseconds whenever a reset takes place.

External Interrupt Request (46) - EIR - This line allows the peripheral to interrupt the computer. The EIR line is active low.

#### **General Purpose**

Control 0 and 1 (22,23) - CTL0, CTL1 - These are general-purpose lines that the computer can set.

Status 0 and 1 (47,48) - STI0, STI1 - These are general-purpose lines that the computer can read.

#### Grounds

Grounds (18,24,26,43,49) - GND - These are the signal grounds. These pins provide the ground potential for the signal lines.

Chassis Ground (25) - CHGND - This pin is connected to the IO bracket that screws into the PC chassis. It is usually used to connect to the cable shield.

# **Differences Between GPIO 600 and GPIO 650**

The GPIO 600 and 650 are both designed to provide the same interface for communication with digital peripherals. All interaction with the peripheral are essentially the same. The differences come from the interaction between the GPIO board and the host computer. There are also some configuration differences.

The GPIO 650 has a 16-bit interface with the host computer and can use DMA to transfer data. The GPIO 600 uses an 8-bit interface and does not support DMA. The wider data path and the available DMA can allow the GPIO 650 to transfer data significantly faster with fast peripherals than the GPIO 600.

Since the GPIO 650 has a 16-bit interface it has access to the high numbered interrupt sources. These higher sources, greater than 9, are more available than the lower sources making it easier to locate a free interrupt channel.

The input clock source is set on both boards with a dip switch but on the GPIO 650 the software can override these settings.

The PCTL delay time is modified on the GPIO 600 by soldering in a capacitor or a resistor. The PCTL delay time for the GPIO 650 is selected from software. This limits the maximum delay on the GPIO 650 to  $1.5\mu$ s while the GPIO 600 can be extended to 100's of microseconds with the use of a large capacitor.

The DOUT clear jumper on the GPIO 600 and switch on the GPIO 650 clears the DOUT lines on reset. With the GPIO 600 this forces the output lines low regardless of the polarity set for the output lines. The GPIO 650 sets the lines to a logical 0. This allows the lines to be set low or left high impedance depending on the polarity set for the lines.

# **Interfacing Circuits**

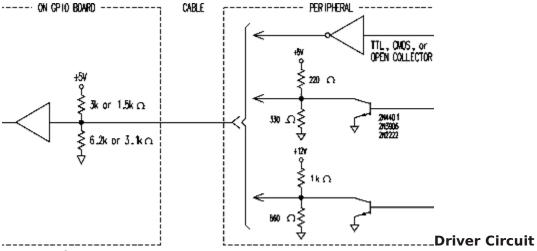

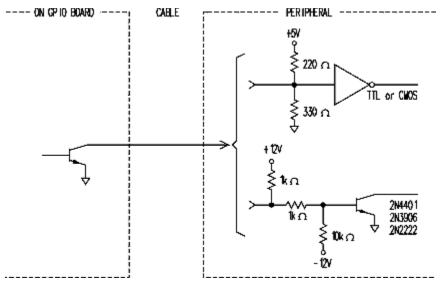

This section gives the electrical requirements for the GPIO interface and some suggestions on interfacing circuits.

# **Peripheral Driver Circuit**

All signal and data input lines are connected to a TTL input. The data lines are pulled up to 3.4V with a  $3k/6.2k\Omega$  resistor divider. The signal lines are pulled up to 3.4V with a  $1.5k/3.1k\Omega$  resistor divider. Input voltages above 5.5V or below -0.5V can result in damage to the GPIO board.

Peripheral Drive Requirements:

Iin low= 2mA - data lines= 4.5mA - signal lines (PFLG, PSTS, STI0, STI1)Vin max= 5.5VVin high> 2.0VVin low< 0.7V - data lines< 0.6V - signal lines

# Suggestions

#### **Peripheral Receiving Circuit**

All of the GPIO outputs, both for signals and data, use open collector output buffers. This means that the line is either left free for a high signal, high impedance, or being pulled to ground for a low signal. This has two effects: first, the computer can write to devices running off any voltage up to 30V, second, the driver must be pulled to the high voltage or the peripheral will probably always read a low.

**GPIO16 Output Driver Specifications:**

| Vout low  | = 0.4V max while sinking 16mA<br>= 0.7V max while sinking 40mA |

|-----------|----------------------------------------------------------------|

| Vout high | = 30V max                                                      |

| Iout low  | = 40mA                                                         |

### **Receiver Circuit Suggestions**

# **Data Settling Times**

The data settling time is the time from when the peripheral or the computer writes the data until that data is valid. The length of the cable and the type of driver affects the settling time for a particular application. If sufficient time is not provided for the data to settle erratic data errors will occur.

### **PCTL Delay Time**

The PCTL delay time sets the time from when the data is written to the output buffers until the PCTL line is set. The transition of PCTL from clear to set, indicates to the peripheral that the data is valid.

On the GPIO 650 the PCTL delay time is set with software from 0-100ns to  $1.4-1.5\mu$ s. Refer to Chapters 3 or 5 for information on setting the PCTL Delay time.

With the GPIO 600 a resistor is added to shorten the delay time. A capacitor is added to lengthen the delay time. The resistor or capacitor must be soldered onto the board. The locations for R4 and C2 are shown in the board diagram in chapter 1.

# **GPIO 600 Equations for PCTL Delay Time**

#### To decrease time constant:

$$R_2 = \frac{3.4e^{-3}}{t_{downer}} - 4700$$

To increase time constant:

$$C_4 = \frac{t_{increase}}{3290}$$

### **Peripheral Delay Time**

The peripheral must also insure that the data is has written is stable at the GPIO board before it latches the data into the input buffers. The peripheral should delay its response with PFLG until the data has settled.

# **Data Handshaking**

Data handshaking is the process of using signals between the computer and peripheral to inform the other when it is ready to receive or transmit data. This section describes the use of the handshaking lines and demonstrates the data flow that these lines allow.

In the following discussion Full and Pulse Mode Handshaking are shown. The selection between Full and Pulse mode is made with the HND switch described in Chapter 1.

For inputs the computer reads the contents of the input data buffers on the GPIO board and not the actual input lines. The clock type determines when the data is loaded into these buffers. A RDY clock loads the buffers on a busy-to-ready transition of PFLG. A BSY clock loads the buffers on a ready-to-busy transition of PFLG. The RD clock loads the buffers as it is reading them. The setting of the switches that control the clock selection is described in Chapter 1. Software can override the input clock source switch settings on the GPIO 650 see Chapters 3 and 5 for the registers to modify.

A BSY or RDY clock would normally be chosen for transfers that use handshaking. These sources allow the user to know exactly when the data is going to be stored in the input buffers.

If the buffers are read without handshaking the RD clock source would normally be used. With the RD clock source the data read would be whatever is on the input lines when the computer reads the input buffers. If the clock source is BSY or RDY and PFLG is not toggled the buffer reads would always return the same value regardless of the input lines because the buffers would never be loaded with new data.

### Handshaking Steps

A complete handshake involves five separate operations that take place in the order listed. The first two are optional depending on the configuration of the board.

**1.** A peripheral OK check can be made before the start of a transfer. The peripheral check consists of the computer reading the PSTS line, if it is a logical 1 the peripheral is considered OK.

**2.** A peripheral ready check can be made before proceeding with the transfer of each word of data. In this case the state of the PFLG line is checked. If PFLG is in the ready state the computer proceeds, if not, the computer waits until the peripheral puts PFLG in the ready state. The PFLG line is checked if Full-Mode handshakes are selected, it is not for Pulse-Mode handshakes.

**3.** The computer initiates the transfer by setting the PCTL and IO lines. The IO line indicates the direction of transfer while PCTL indicates the start of a handshake.

**4.** The peripheral reads the data output lines or writes information to the data input lines.

**5.** The peripheral acknowledges that it has read or written the data. It does this by setting or clearing the PFLG line.

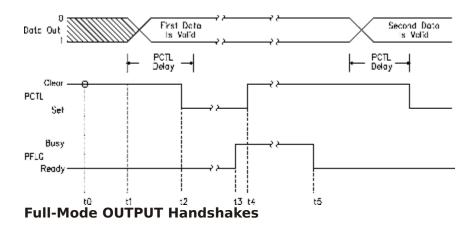

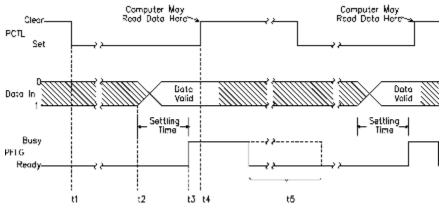

### **Timing Diagrams**

In the following pages the possible configurations for the Full and Pulse Mode input and output handshakes are illustrated and described. Since the IO line is always set high for a read and low for a write it will not be shown. The peripheral OK check will not be illustrated.

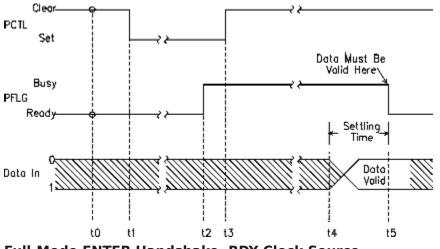

t0 - The computer waits until PCTL is clear and PFLG is ready before starting the transfer.

t1 - The computer puts the data on the output lines and sets the IO line low.

t2 - After the PCTL delay time has expired, PCTL is set. This indicates to the peripheral that there is valid data.

t3 - The peripheral sets PFLG to busy.

t4 - The ready to busy transition on PFLG clears the PCTL line.

t5 - The peripheral sets PFLG to ready.

Because the interface is set to full-mode the peripheral can read the data at any time from the falling edge of PCTL until the busy-to-ready transition of PFLG. The data stays valid since the interface will not change the output data until the interface returns to the ready condition of PCTL clear and PFLG ready.

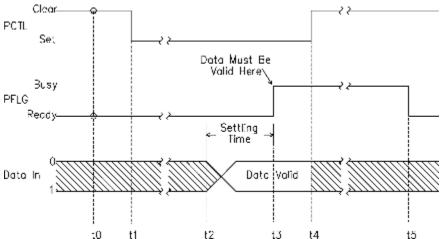

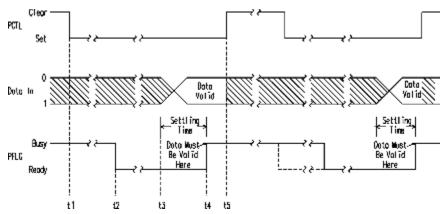

### Full-Mode ENTER Handshake, BSY Clock Source

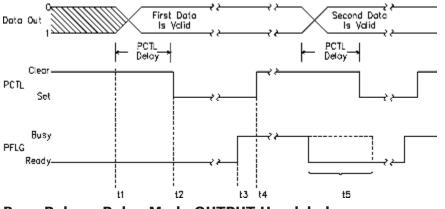

t0 - The computer checks to see if the peripheral is ready. Since PCTL is clear and PFLG is ready the transfer can proceed.

t1 - The computer sets PCTL to start the transfer. The IO line is simultaneously set high.

t2 - The peripheral places the data on the input lines.

t3 - After the data lines have had time to settle the peripheral sets PFLG. The setting of PFLG clocks the data into the input buffers on the GPIO board.

t4 - The PCTL line is cleared automatically after PFLG goes busy.

t5 - The peripheral sets PFLG ready. Once PFLG is ready the peripheral is ready to start a new transfer.

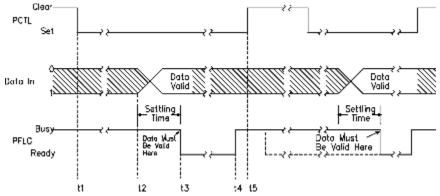

Full-Mode ENTER Handshake, RDY Clock Source

t0 - The computer checks to see if the peripheral is ready. Since PCTL is clear and PFLG is ready the transfer can proceed.

t1 - The computer sets PCTL to start the transfer. The IO line is simultaneously set high if it was not already high.

t2 - The peripheral sets PFLG busy.

t3 - PCTL is cleared in response to PFLG being set to busy.

t4 - The peripheral puts the data on the input lines. This can be done simultaneously with PFLG being set to busy.

t5 - The peripheral sets PFLG ready after the data lines have had time to settle. The transaction of PFLG from busy to ready will clock the data into the buffers on the GPIO board. This also puts the interface in the ready state to start a new transfer.

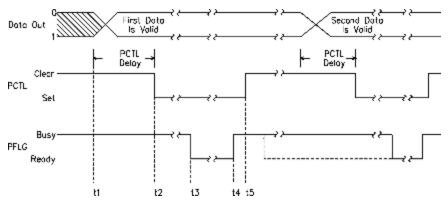

**Busy Pulses, Pulse-Mode OUTPUT Handshakes**

With the interface set to pulse-mode transfers, the computer will initiate the transfer if PCTL is clear regardless of the state of PFLG.

t1 - The computer puts the data on the data out lines and sets the IO line low.

t2 - After the PCTL delay time has expired, the PCTL line is set. This indicates that the data is valid.

t3 - The peripheral reads the data then acknowledges the transfer by setting PFLG to busy.

t4 - The PCTL line is cleared by the PFLG ready-to-busy transition. Once PCTL is clear the computer is ready to start a new transfer.

t5 - It is not important when PFLG goes ready since the computer will start a new transfer even if it is busy.

### Ready Pulses, Pulse-Mode OUTPUT Handshakes

The computer will initiate the transfer if PCTL is clear regardless of the state of PFLG.

t1 - The computer puts the data on the output lines and sets the IO line low.

t2 - After the PCTL delay time has expired, the PCTL line is set. This indicates the presence of valid data on the output data lines.

t3 - The peripheral puts PFLG in the ready state.

t4 - The peripheral completes the handshake by setting PFLG busy. This ready-to-busy transition clears the PCTL line. The peripheral should read the data before the PFLG ready-to-busy transition.

t5 - Once PCTL is clear the computer is ready to start a new transfer.

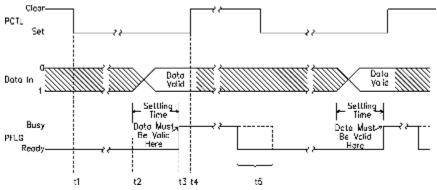

### Busy Pulses, Pulse-Mode ENTER (BSY Clock Source)

The computer will initiate the transfer if PCTL is clear regardless of the state of PFLG.

t1 - The computer sets PCTL and the IO line is set high.

t2 - The peripheral writes the data onto the data input lines.

t3 - After a data settling time the peripheral sets PFLG to busy. This clocks the data into the GPIO board buffers.

t4 - The PCTL line goes clear due to the ready-to-busy transition.

t5 - Some time later the PFLG line returns to ready. The next transfer start will not wait for this action.

Busy Pulses, Pulse-Mode ENTER (RDY Clock Source)

The computer will initiate the transfer if PCTL is clear regardless of the state of PFLG.

- t1 The computer sets PCTL and the IO line is set high.

- t2 The peripheral writes the data onto the data input lines.

- t3 The peripheral sets PFLG to busy.

t4 - The PCTL line goes clear due to the PFLG ready-to-busy transition. At this point the computer considers the transaction complete and might read the buffers even though the data has not yet been clocked in.

t5 - The PFLG line returns to ready clocking the data into the GPIO board buffers.

Note: DO NOT USE THIS TRANSFER MODE. There is no way to guarantee that the peripheral can clock the data into the input data buffers before the computer reads the buffers. When the input data buffers are clocked late the data read will be from the previous handshake.

Ready Pulses, Pulse-Mode ENTER (BSY Clock Source)

The computer will initiate the transfer if PCTL is clear regardless of the state of PFLG.

t1 - The computer sets PCTL and the IO line is set high.

t2 - The peripheral sets PFLG to ready.

t3 - The peripheral writes its data to the input lines.

t4 - After the data has had time to settle the peripheral sets the PFLG line to busy. This transaction will clock the data into the input buffers on the GPIO board.

t5 - In response to the ready-to-busy transition on the PFLG line, PCTL is cleared and the interface is ready to initiate another transfer.

Ready Pulses, Pulse-Mode ENTER (RDY Clock Source)

The computer will initiate the transfer if PCTL is clear regardless of the state of PFLG.

- t1 The computer sets PCTL and the IO line is set high.

- t2 The peripheral writes the data to the input lines.

t3 - After the data has had time to settle the peripheral sets the PFLG line to ready. This transaction will clock the data into the input buffers on the GPIO board.

t4 - The peripheral will later set PFLG to busy.

t5 - In response to the ready-to-busy transition on the PFLG line, PCTL is cleared and the interface is ready to initiate another transfer.

# **General Purpose IO Lines**

These lines are not used for handshaking and are available as aids in working with the peripheral. The usual purpose of each line is described.

### **PSTS Line**

This is the peripheral status line. It can be used to check that the peripheral is still active or at least that the cable is still connected. The typical use is to have the peripheral pull the PSTS line to ground. The PSTS polarity is set so that low represents peripheral OK. If the cable becomes disconnected the line floats high due to the on-board pull-up resistors which causes the PSTS line to report that the peripheral is not OK.

### **PRESET Line**

This is the peripheral reset line. When the board is reset this line pulses low for at least  $15\mu$ s. This allows both the GPIO 650 and the peripheral to be reset at the same time. A reset is generally performed every time a new program that uses the board is run.

### **EIR line**

This is the external interrupt request line. The board can be configured in software to cause an interrupt whenever this line is low. This lets the peripheral tell the computer when it needs attention. If not used as an interrupt source the EIR line can be used as a generalpurpose input.

### **CTL0 and CLT1 Lines**

These are the control 0 and control 1 lines. They have no predefined purpose but can be set and cleared from software as desired.

### STI0 and STI1 Lines

These are the status 0 and status 1 lines. They have no predefined purpose but can be read from software as desired.

# Interrupts

Interrupts are used to interrupt the computations that the computer is performing so that some other action can take place. The typical action with the GPIO 650 is the start or continuation of the transfer of data. Each interrupt source is enabled and disabled from software.

### Interrupt Sources

- Interface Ready

- External Interrupt Request (EIR)

- DMA Terminal Count (GPIO 650 only)

### **Interface Ready**

This interrupt source becomes active whenever the interface is ready to start a new handshake. The interface is ready if PCTL is clear with pulse mode handshake or when PCTL is clear and PFLG is ready with full mode handshake.

Software drivers may use this interrupt when controlling transfers. To avoid conflicting with the software drivers do not enable this source while the driver is performing a transfer.

### **External Interrupt Request**

The EIR line is the source for this interrupt. When the EIR line is low and External Interrupt Request is enabled an interrupt is be generated. This is generally used by the peripheral to inform the computer that it needs attention.

This interrupt source is not used by the software drivers and may be active at any desired time without conflicting with the driver.

#### **DMA** Terminal Count

This interrupt source is used by the software driver to control DMA transfers on the GPIO 650. Since it is used exclusively with DMA, TransEra supplied software drivers do not make it available to the user. Information on this interrupt is in Chapter 5 Programming Guide for GPIO 650.

# **DMA Transfers**

DMA stands for Direct Memory Access. DMA is not supported on the GPIO 600. These transfers use a DMA controller on the computer to move the data between the GPIO board and the computers memory without using the computers CPU. DMA transfers are not as subject to the variable delays that exist with Interrupt or Polled (CPU controlled) transfers.

Using DMA is generally the fastest way to perform large transfers of data. Small transfers may be faster with polled transfers because of the time it takes to configure the DMA controller. TransEra supplied software drivers selects the transfer mode that is expected to be the fastest.

When performing 8-bit transfers with the peripheral the GPIO 650 performs two handshakes and then transfers the data with a single 16-bit DMA transfer. This doubles the maximum transfer rate with 8-bit peripherals.

The memory structure of a PC and the limitations of the DMA controller, limits the amount of data that can be transferred with a single DMA controller configuration from 1 to 65536 words. Where in the range a specific transfer starts depends on the physical location in memory that the data is using. When the DMA controller reaches that configuration's limit it needs to be reconfigured. While the DMA controller is being reconfigured transfers with the peripheral are paused. The user will generally not be able to predict when these pauses will take place.

With the exception of the pause mentioned above, the maximum time that the computer should take to get ready for the next handshake is  $4\mu s$ . With polled and interrupt modes the time for the computer to get ready can vary greatly depending on the speed of the machine and the resources that are in use.

# Reset

Before using the GPIO board it is recommended that the board be reset. This puts the board and interface into a known state before accessing the interface. When the board is reset a reset pulse of at least  $15\mu$ s is put on the PRESET line to inform the peripheral that a reset

has taken place.

# **Chapter 3 HTBasic Software Interface**

This chapter explains how to use the GPIO board with HTBasic and the HTBasic software driver. HTBasic version 3.1d or later is required to run the driver for the GPIO 600. Version 4.0 or later is needed for the GPIO 650 driver.

The interface is designed to duplicate the operation of the HP GPIO 98622A as close as possible so that few if any software changes need to be made when using either the GPIO 600 or GPIO 650 boards with HTBasic in place of the HP GPIO 98622A with RMB. The differences between the two systems are summarized in the section Differences Between TransEra and HP GPIO.

# **Differences Between TransEra and HP GPIO**

This section gives the differences between the HP GPIO 98622A and the TransEra GPIO Boards.

### Setup

TransEra 600 and 650: Board address must be set with dip switches for the PC. HP: No address needs to be selected.

TransEra 600 and 650: ISC is set in software during the LOAD BIN command. HP: ISC is selected with a dip switch.

TransEra 600 and 650: The interrupt is selected from software in the LOAD BIN command. HP: An interrupt priority is selected with a dip switch.

TransEra 600: Identical to HP. TransEra 650: The PCTL delay time is set from software. HP: A resistor or capacitor is added to change the PCTL delay time.

TransEra 600: Does not support DMA. TransEra 650: The DMA channel is selected from software in the LOAD BIN command. HP: The DMA channel is selected with a DIP switch.

### Operation

TransEra: Unused bits in Status and Readio registers are set to zero. HP: Unused bits in Status registers are set to zero while unused bits in Readio registers are generally set to one.

TransEra 600: Used a DOUT CLEAR jumper but the output lines are set low regardless of the selected polarity.

TransEra 650: When in the on position the DCLR switch causes the data output lines to be set to a logical zero.

HP: Uses the DOUT CLEAR jumper to perform the same function as the GPIO 650.

### Registers

TransEra 600: Does not use bits 0-5 of the Interrupt and DMA Status register. TransEra 650: Does not use bits 1-5 of the Interrupt and DMA Status register and bit 0 reports if DMA is active.

HP: The Interrupt and DMA Status register uses these bits differently.

TransEra 600: Same as HP.

TransEra 650: Defines an Input Clock Source register to override the switch selected input

clock sources. HP: Does not have this register.

# **Control Registers**

This section lists the control registers and explains the purpose of the control bits. These registers should be used instead of writeio registers for board control. All registers are 8-bit unless otherwise noted.

The value associated with each bit is the decimal representation of that bit being set.

| Control Registers |                                    |  |  |  |

|-------------------|------------------------------------|--|--|--|

| <u>Register</u>   | Name                               |  |  |  |

| 0                 | Interface Reset                    |  |  |  |

| 1                 | Set PCTL                           |  |  |  |

| 2                 | Peripheral Control                 |  |  |  |

| 3                 | Data Out (16-bits)                 |  |  |  |

| 4                 | Input Clock Source (GPIO 650 only) |  |  |  |

| -                 | Interrupt Enable                   |  |  |  |

### **Reset Interface**

**CONTROL Register 0**

Writing a non-zero value to this register resets the interface.

### Set PCTL

**CONTROL Register 1**

Writing a non-zero value to this register sets PCTL.

### **Peripheral Control**

**CONTROL Register 2**

Bit 7Bit 6Bit 5Bit 4Bit 3Bit 2Bit 1Bit 0Value=128 Value = 64 Value = 32 Value = 16Value = 8Value = 4Value = 2Value = 10Report<br/>PSTS ErrorSet CTL1<br/>LowSet CTL0<br/>Low

Bit 0: Set CTL0 Low When this bit is set the CTL0 line is driven low. When clear, the CTL0 output is in a high impedance state.

Bit 1: Set CTL1 Low When this bit is set the CTL1 line is driven low. When clear the CTL1 output is in a high impedance state.

Bit 2: Report PSTS Error When set the interface will check the PSTS line before that start of each transfer. When clear the status of the PSTS line is ignored.

### Data Out (16 bits)

CONTROL Register 3

Bit 15 Bit 14 Bit 13 Bit 12 Bit 11 Bit 10 Bit 9 Bit 8

| D015  | D014  | D013  | D012  | D011  | DO10  | DO9   | DO8   |

|-------|-------|-------|-------|-------|-------|-------|-------|

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

| D07   | D06   | DO5   | DO4   | DO3   | D02   | DO1   | DO0   |

This is the output data buffer. Each bit is output on the corresponding output line. The logic polarity is user selectable with switch 1.

#### **Interface Parameters**

Control Register 4 (not present on GPIO 600 or HP 98622A)

Bit 7Bit 6Bit 5Bit 4Bit 3Bit 2Bit 1Bit 0Value=128 Value = 64 Value = 32 Value = 16Value = 8Value = 4Value = 2Value = 10Clock Source<br/>High ByteClock Source<br/>Low Byte

Bits 0,1: Clock Source Low Byte

These bits select the input clock source for the low byte data buffer. These bits are cleared on LOAD BIN or reset. When clear, the switch 2 setting are used.

#### Bits 1-0 Clock Source

| 00 | Switch Setting |

|----|----------------|

| 01 | RDY            |

| 10 | BSY            |

| 11 | RD             |

|    |                |

Bits 2,3: Clock Source High Byte

These bits select the input clock source for the high byte data buffer. These bits are cleared on LOAD BIN or reset. When clear, the switch 2 setting are used.

#### Bits 3-2 Clock Source

| 00 | Switch Setting |

|----|----------------|

| 01 | RDY            |

| 10 | BSY            |

| 11 | RD             |

#### **Interrupt Enable**

Interrupt Enable Register

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 Value=128 Value = 64 Value = 32 Value = 16 Value = 8 Value = 4 Value = 2 Value = 1 0 Enable Enable Interface EIR Ready Interrupts Interrupts

Bit 0: Enable Interface Ready Interrupts

When set, an interrupt is requested when the interface is ready. When clear, this interrupt source is disabled.

Bit 1: Enable EIR Interrupts

When set, an interrupt is requested when the EIR line is low. When clear, this interrupt source is disabled.

# **Status Registers**

This section lists the status registers and explains what each bit returns. These registers should be used instead of readio registers for board control. All registers are 8-bit unless otherwise noted.

Status Registers

| Register | Name                     |

|----------|--------------------------|

| 0        | Card Identification      |

| 1        | Interrupt and DMA Status |

| 2        | Board Status             |

| 3        | Data In (16-bit)         |

| 4        | Interface Ready          |

| 5        | Peripheral Status        |

### **Card Identification**

STATUS Register 0

Reading this register returns the ID number of the GPIO driver. The ID number for the GPIO driver is 3.

### **Interrupt and DMA Status**

**STATUS Register 1**

Bit 7Bit 6Bit 5Bit 4Bit 3Bit 2Bit 1Bit 0Value=128Value = 64Value = 32Value = 16Value = 8Value = 4Value = 2Value = 1

| Interrupts Interrupt is | Undefined | DMA is |

|-------------------------|-----------|--------|

| Are Requested           |           | Active |

| Enabled                 |           |        |

Bit 0: DMA is Active

A DMA transfer is being performed. If clear DMA is not active. This bit is undefined on the GPIO 600.

Bit 6: Interrupt is Requested If set an interrupt is currently requested. If clear no interrupts are requested.

Bit 7: Interrupts are Enabled If set at least one interrupt source is enabled. If clear no interrupt sources are enabled.

### **Transfer Status**

**STATUS Register 2**

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 Value=12 Value = 64 Value = 32 Value = 16 Value = 8 Value = 4 Value = 2 Value = 1 8 Undefined Handshake Interrupts Transfer In Are In Progress Enabled Progress

Bit 0: Transfer in Progress If set a transfer is taking place. If clear a transfer is not active.

### Bit 1: Interrupts are Enabled

This is the same as bit 7 of the Interrupt and DMA Status register. If set at least one interrupt source is enabled. If clear no interrupt sources are enabled.

Bit 2: Handshake in Process

If set a handshake is in progress. With pulse mode handshakes that means that PCTL is set. With full mode handshakes PTCL is set or PFLG is busy. If clear a handshake is not taking place.

#### Data In (16 bits)

**STATUS Register 3**

| Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 |

|--------|--------|--------|--------|--------|--------|-------|-------|

| DI15   | DI14   | DI13   | DI12   | DI11   | DI10   | D19   | DI8   |

|        |        |        |        |        |        |       |       |

| Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1 | Bit 0 |

| DI7    | DI6    | DI5    | DI4    | DI3    | DI2    | DI1   | DI0   |

This register returns the value stored in the input buffers. The input buffers are updated according to the input clock source selected for each byte.

#### **Interface Ready**

**STATUS Register 4**

If set the interface is ready for a subsequent data transfer. If clear the interface is busy.

#### **Peripheral Status**

**STATUS Register 5**

Bit 7Bit 6Bit 5Bit 4Bit 3Bit 2Bit 1Bit 0Value=128 Value = 64 Value = 32 Value = 16Value = 8Value = 4Value = 2Value = 1

Undefined PSTS EIR STI1 STI0 OK Line Low Line Low Line Low

Bit 0: STIO Line Low If set the STIO line is low. If clear the line is high.

Bit 1: STI1 Line Low If set the STI1 line is low. If clear the line is high.

Bit 2: EIR Line Low If set the EIR line is low. If clear the EIR line is high.

Bit 3: PSTS OK If set the PSTS line is OK. The polarity of the PSTS line is user selectable with switch 1. If clear the PSTS line is not OK.

# LOAD BIN

The LOAD BIN command loads the software driver that HTBasic uses to communicate with the GPIO board. It must be executed before any access to the board from HTBasic.

The 600 card is supported with HTBasic for Windows under Windows 95/98/ME & NT 4.0. To load the card under 95/98/ME, use the GPIO.DW6 driver. For loading the driver under Windows NT, please see the Installing and Using Manual, Chapter 6, under Loading a Kernel Level Driver.

For HTBasic for Windows, the 650 card is only supported under NT 4.0. To load this driver

please see the Installing and Using Manual, Chapter 6, under Loading a Kernel Level Driver.

For the DOS version, the driver filenames that the LOAD BIN uses for the GPIO 600 are 'gpio.d86' for the PC version and 'gpio.d36' for the 386 version. For the GPIO 650 the filenames are 'gpio16.d86' for the PC version and 'gpio16.d36' for the 386 version.

If the default value is used that parameter does not need to be specified in the LOAD BIN command.

#### **LOAD BIN Options**

| Parameter        | Default Value | Range               |

|------------------|---------------|---------------------|

| BASE             | 380 (hex)     | 200-3F0 (hex)       |

| ISC              | 12            | 4-32                |

| INT (GPIO 600)   | 5             | 0,2,3,4,5,6,7       |

| INT (GPIO 650)   | 10            | 0,5,7,9,10,11,12,15 |

| DMA (GPIO 650)   | 6             | 0,5,6,7             |

| DELAY (GPIO 650) | 1             | 0-7                 |

The address set with the IO Address switch must match the BASE address value used for LOAD BIN. If these do not agree the LOAD BIN will give a device not found error.

The default ISC for the GPIO board is 12. This is the same ISC number assigned to the second parallel port. If the computer has a second parallel port the ISC of the GPIO board should be changed.

Interrupts may be disabled by using a 0 as the interrupt value. If interrupts are disabled the board will not support TRANSFER commands and ENTER and OUTPUT commands could be slower.

DMA transfers are only supported on the GPIO 650. An interrupt channel must be specified for DMA to be used. DMA is not supported on the GPIO 600.

The DELAY option controls the PCTL delay time for the GPIO 650. This delay is the time from when the computer outputs the data onto the GPIO cable until the PCTL line is set. If set to a time shorter than the data settling time there can be data errors on outputs. A resistor or capacitor is added to the board to change the PCTL delay time for the GPIO 600.

#### Value Delay Time

- 0 0-100ns

- 1 200-300ns

- 2 400-500ns

- 3 600-700ns

- 4 800-9 00ns

- 5 1.0-1.1μs

- 6 1.2-1.3μs

- 7 1.4-1.5 μs

An example LOAD BIN for the GPIO 650 with a base address of 220 hex, ISC number of 13, using interrupt channel 15 and DMA channel 6 with a PCTL delay of 400-500ns.

LOAD BIN "GPI016; BASE 220 ISC 13 INT 15 DMA 6 DELAY 2"

The LOAD BIN for the GPIO 600 would be the same except the DMA and DELAY parameters would be left off and the INT parameter must match the jumper location.

# **Interface Reset**

The interface should be reset before use to put the interface into a known state. It is reset when the CLR I/O or BASIC RESET key is pressed and when the LOAD BIN command is executed. The interface can be also be reset in software by writing a one to Reset Interface (control register 0).

The following occurs during a reset:

- The Peripheral Reset line (PRESET) is pulsed low for at least 15µs.

- The PCTL line is cleared.

- The interrupt enable bit is cleared. This disables interrupts until re-enabled.

- If the DCLR switch is set, the Data Out lines are set to a logic low on the GPIO 650. If the DOUT CLEAR jumper is set on the GPIO 600 the Data Out lines are set low.

• For the GPIO 650, the clock source high and low bits of Interface Parameters (control register 4) are set to 0. This forces the clock source to the switch two settings.

The following lines are unchanged by a reset:

- The CTL0 and CTL1 output lines.

- The IO line.

- The Data Out lines (if DCLR or DOUT CLEAR JUMPER is not set).

# **Using STATUS and CONTROL Commands for I/O**

Reading status register three returns the value of the data buffers in 16-bit 2's complement (-32768 to 32767). The value of these buffers depends on the clock source selected. With the RD source the buffers will be clocked just before reading so that the value read reflects the value on the input data lines. If RDY or BSY source is selected the value will be whatever was present during the previous handshake. The IO line is set high to indicate that a read is taking place. The status command does not use handshaking, therefore, it will not set PCTL to initiate a handshake.

### **STATUS Example**

|    |                 | DI15-DI8 | DI7-DI0 |

|----|-----------------|----------|---------|

| 10 | Gpio=12         |          |         |

| 20 | STATUS Gpio,3;A | 2        | 3       |

| 30 | STATUS Gpio,3;B | 255      | 255     |

With the RD clock source A = 515 (i.e.,  $256 \times 2 + 3$ ) and B = -1.

Writing to control register three sets the data lines to the indicated value. The value is represented in 16-bit 2's complement (-32768 to 32767). The IO line will be set low to indicate that an output was performed. No handshaking takes place since PCTL will not be set.

#### **CONTROL Example**

|    |                         | D015-D08 | D07-D00 |

|----|-------------------------|----------|---------|

| 10 | Gpio=12                 |          |         |

| 20 | CONTROL Gpio,3;5*256+11 | 5        | 11      |

| 30 | CONTROL Gpio,3;-2       | 255      | 254     |

Status and Control registers can be used to control user defined handshaking. The following example demonstrates the use of the STATUS and CONTROL statements to perform handshaking with the CTL0, STI0, and IO lines. STI0 will not be able to clock the data into the input buffers since only PFLG is connected to the clocks but it can be used to indicate when there is valid data on the lines to be read. The RD clock source is required so that a status

read will clock the data line values into the buffers before reading them.

### **User Handshake Example**

```

10

Gpio=12

20

Num samples=10

30

DIM Samples(10)

40

STATUS Gpio,3;Tmp

! Perform a dummy read to set IO high

50

FOR I=1 TO 10

! This reads 10 data points

CONTROL Gpio,2;1 ! Set CTL0 to request communication

60

70 Loop1: Status GPIO,5;Stat5

! Wait until peripheral sets STI0

80

IF NOT BIT(Stat5,0) THEN GOTO Loop1

90

STATUS Gpio,3;Samples(I) ! Read data point

100

CONTROL Gpio,2;0 ! Clear CTL0 to indicate data has been read

110 Loop2: STATUS Gpio,5;Stat5

! Wait for STIO to be cleared

IF BIT(Stat5,0) THEN GOTO Loop2 ! For a full handshake

120

130

NEXT I

```

# **Using OUTPUT and ENTER**

Whenever the OUTPUT or ENTER command is used a complete handshake is required. If the handshake does not occur HTBasic gives one of following two responses: 1) If a timeout is set the interface will wait the allotted time then give a timeout error. 2) If the timeout period is not set the computer will appear to have locked up. Pressing the CLR I/O key restores control to the user. The default for the GPIO board is to not have the timeout set.

Most of the examples are of OUTPUT statements. ENTER statements require the same data on the same data lines that the OUTPUT statements produce.

The GPIO interface defaults to an 8-bit transfer unless otherwise specified.

The ASCII representations for A, B, and C are 65, 66, and 67 respectively. Carriage Return is 13 and Line Feed is 10. All values shown are in decimal.

### **OUTPUT String Example**

|    |                  | D015-D08 | D07-D00 |

|----|------------------|----------|---------|

| 10 | Gpio=12          |          |         |

| 20 | OUTPUT Gpio;"AB" | 0        | 65      |

|    |                  | 0        | 66      |

|    |                  | 0        | 13      |

|    |                  | 0        | 10      |

Only the low 8 bits are used for default transfers, Carriage Return Line Feed is the default delimiter.

#### **OUTPUT Multiple Strings Example**

|    |                      | D015-D08 | D07-D00 |

|----|----------------------|----------|---------|

| 10 | Gpio=12              |          |         |

| 20 | OUTPUT Gpio;"AB";"C" | 0        | 65      |

|    |                      | 0        | 66      |

|    |                      | 0        | 67      |

|    |                      | 0        | 13      |

|    |                      | 0        | 10      |

Multiple strings are combined before outputting.

#### **OUTPUT Word Default Delimiter**

|    |                                | D015-D08 | D07-D00 |

|----|--------------------------------|----------|---------|

| 10 | Gpio=12                        |          |         |

| 20 | OUTPUT Gpio USING "W";5*256+15 | 5        | 15      |

|    |                                | 0        | 13      |

|    |                                | 0        | 10      |

|    |                                |          |         |

The default delimiter (byte mode) is still in effect.

### **OUTPUT Word No Delimiter**

|    |                                  | D015-D08 | D07-D00 |

|----|----------------------------------|----------|---------|

| 10 | Gpio=12                          |          |         |

| 20 | OUTPUT Gpio USING "W,#";5*256+15 | 5        | 15      |

| 30 | OUTPUT Gpio USING "W,#";-1       | 255      | 255     |

Numbers are output in 2's complement 16-bit integers (-32768 to 32767).

# **OUTPUT Strings With Word Example**

|    |                                   | D015-D08 | D07-D00 |

|----|-----------------------------------|----------|---------|

| 10 | ASSIGN @Gpio TO 12;WORD,FORMAT ON | I        |         |

| 20 | OUTPUT @Gpio;"A";"BC"             | 65       | 66      |

|    |                                   | 67       | 13      |

|    |                                   | 10       | 0       |

This transfer method would normally not be used due to the difficulty of having the peripheral reorganize the data.

### **OUTPUT Word Format Off Example**

|    |        |                               | D015-D08 | D07-D00 |

|----|--------|-------------------------------|----------|---------|

| 10 | ASSIGN | @Gpio TO 12; WORD, FORMAT OFF | ,        |         |

| 20 | OUTPUT | @Gpio;5*256+11                | 5        | 11      |

| 30 | OUTPUT | @Gpio;-2                      | 255      | 254     |

WORD,FORMAT OFF is equivalent to "W,#". This will execute the transfer of data 5-10 times faster than if the USING "W,#" were used.

### **OUTPUT Array Example**

|    |                                    | D015-D08 | D07-D00 |

|----|------------------------------------|----------|---------|

| 10 | INTEGER I(10)                      |          |         |

| 20 | MAT I=(3*256+7)                    |          |         |

| 30 | ASSIGN @Gpio TO 12;WORD,FORMAT OFF |          |         |

| 40 | OUTPUT @Gpio;I(*)                  | 3        | 7       |

|    |                                    | 3        | 7       |

|    |                                    | ETC.     |         |

Arrays can be output with a single statement. By default HTBasic arrays are 0 based. This causes the above example to output 11 I(0)-I(10) words of data.

ENTER statements expect the same data, on the same numbered data input lines that a corresponding output statement produces.

#### **ENTER Array Example**

| 10 | INTEGER I(10)                      |      |   |

|----|------------------------------------|------|---|

| 20 | ASSIGN @Gpio TO 12;WORD,FORMAT OFF | ,    |   |

| 30 | ENTER @Gpio;I(*)                   | 3    | 7 |

|    |                                    | 3    | 7 |

|    |                                    | ETC. |   |

Eleven handshakes complete the above transfer since INTEGER I(10) creates an array with eleven elements After the transfer, all entries of array "i" will contain 775 (i.e., 3X256 + 7).

# Using the TRANSFER Command

The TRANSFER command allows data to be exchanged (similar to INPUT and OUTPUT commands) with the GPIO through I/O paths. The main difference between TRANSFER and INPUT/OUTPUT statements is TRANSFER can allow other HTBasic commands to be executed as it is executing. A TRANSFER can be thought of as a "background" process. A complete handshake is required when using TRANSFER. A timeout will only occur if the WAIT parameter is specified in the TRANSFER statement.

The following program reads 8 bytes using the TRANSFER statement at line 90. Every 4 bytes read will cause the subroutine at line 170 to be executed. After 2 records are read the transfer will be terminated and the subroutine at line 190 will be executed. Notice that HTBasic continues to execute after the TRANSFER statement is started.

### Input TRANSFER Example

```

10

Gpio=12

INTEGER Xx, I, Cnt, Done

20

30

DIM X$[8] BUFFER

! Create the buffer

40

ASSIGN @Buf TO BUFFER X$; FORMAT OFF

50

ASSIGN @Dev TO Gpio

60

Done=0

70

ON EOR @Dev GOSUB 170 ! Set up end of record gosub

ON EOT @Dev GOSUB 190 ! Set up end of transfer gosub

80

85

! Transfer 2 four byte records

TRANSFER @Dev TO @Buf;RECORDS 2,EOR (COUNT 4)

90

100

IF Done=0 THEN 100

110

STATUS @Buf,4;Cnt

! Read number of bytes in buffer

120

FOR I=1 TO Cnt

ENTER @Buf USING "#,B";Xx ! Read data from the buffer

130

140

PRINT USING "#,K,B,K,/";"[",Xx,"]"

150

NEXT I

PAUSE

160

170

PRINT "END OF RECORD"

180

RETURN

190

PRINT "END OF TRANSFER"

200

Done=1

210

RETURN

220

END

```

The following program outputs 8 bytes (4 words) to the GPIO. The ON EOR statement at line 90 will cause the subroutine at line 160 to be executed every 4 bytes transferred. The ON EOT statement at line 100 causes the subroutine at line 180 when the transfer is done. The data will be output one word (16 bits) at a time (4 handshake transfers). The first transfer will output 49 ("1") on D0-D7 and 50 ("2") on D8-D15.

### **Output TRANSFER Example**

10 Gpio=12 20 INTEGER Bytes, I, Done 30 DIM X\$[8] BUFFER ! Create the buffer 40 Bytes=8 50 ASSIGN @Buf TO BUFFER X\$; FORMAT OFF 60 ASSIGN @Dev TO Gpio;WORD 65 ! Load the buffer with a string 70 OUTPUT @Buf USING "#,K";"12345678" 80 Done=0 90 ON EOR @Dev GOSUB 160 ! Set up the end of record gosub 100 ON EOT @Dev GOSUB 180 ! Set up the end of transfer gosub 110 PRINT "START TRANSFER" ! Transfer 2 four byte records 115 120 TRANSFER @Buf TO @Dev;EOR (COUNT 4) 130 WHILE Done=0 END WHILE 140 150 PAUSE PRINT "END OF RECORD" 160 170 RETURN PRINT "END OF TRANSFER" 180 190 Done=1 200 RETURN 210 END

# Maximizing the Speed of I/O Transfers

For many users the transfer rate of the GPIO board is not relevant since they are passing relatively small amounts of data and the board is fast enough. In other cases transfer rate can be critical. This section lists some ideas to help increase the transfer rate. These techniques are not always applicable but when used can increase performance 2-10 times verses other methods that perform the same task.

Assign a DMA channel to the GPIO interface if using the GPIO 650. When the board is allowed to use DMA the transfer will be able to move data at a rate of 250K word/second. Although pauses will occur in the transfer every 64K words to reinitialize the DMA controller it is still the fastest way to transfer with most machines. Note that timeouts are disabled during DMA transfers.

Avoid the use of USING statements with OUTPUT and ENTER commands. When USING is defined HTBasic handles the transfer in a way that allows it to reformat the data if necessary. This occurs even if it does not reformat the data. This handling adds a large amount of overhead to the transfer. For an example, assigning FORMAT OFF, WORD to the GPIO device will execute outputs about 10 times faster than if USING "W,#" were specified in the OUTPUT statement. In both cases the output data will be the same.

The use of delimiting for ENTER and TRANSFER strings is usually required but the overhead of checking every byte to see if it is the delimiting character slows the transfer significantly. When the length of the data is known use COUNT with TRANSFERs. With ENTERs, ALLOCATE the array to the size of the data and then ENTER into that array.

HTBasic is very flexible when it comes to changing the type of data that is being used. This ability to change the data type can also result in significant overhead. When possible define arrays as integers and use the FORMAT OFF mode to transfer numeric data to the peripheral. If not specified the HTBasic default is FORMAT ON which converts the data into its ASCII representation before outputting it. This results in a large speed penalty.

These techniques are not limited to the exact situations described but the ideas of using DMA, not delimiting, using FORMAT OFF and avoiding data type changes can increase the data rate for many applications.

# **GPIO Timeouts**

Timeouts are used to prevent the system from appearing to lock up when communication with the peripheral is not functioning.

The timeout period starts when PCTL is set and continues until the interface is ready. With a Pulse-Mode transfer it continues until PCTL is clear. For a Full-Mode transfer it continues until PCTL is clear and PFLG is ready.

When a timeout occurs the interface is reset. Refer to Interface Reset for a list of changes on reset. If the error is not trapped with an ON TIMEOUT instruction the program will terminate and display a timeout error.

When using DMA, timeouts are disabled. If the interface stops communicating during a transfer the computer can appear to lock up. Pressing the BASIC RESET key will terminate the program and return control to the user. If this is unacceptable DMA must be disabled by selecting DMA channel 0 when performing the LOAD BIN statement.

# **General Purpose Lines**

There are four general-purpose lines that are available for any use. CTL1 and CTL0 are output lines and STI1 and STI0 are input lines. The lines are read and written to through status and control statements.

### **Peripheral Control**

The CTLx lines are set by writing to Peripheral Control (control register 2). When writing to this register all the bits are modified. To avoid accidentally clearing other bits a software copy of the register should be kept. When a CTLx line it to be changed, bit modify the software copy and then write it to the control register. Note that CTLx has low-true polarity (1 = low). This polarity is not selectable.

### **CTLx Control Example**

```

10Gpio=12! 12 = Interface Select Code20Pcontrol=BINIOR(Pcontrol,1)! Set CTL025! Clear a bit by ANDing the register with the compliment30Pcontrol=BINAND(Pcontrol,BINCMP(2))! Clear CTL140CONTROL Gpio,2;Pcontrol! Write out value

```

This sets the CTL0 bit and clears the CTL1 bit in line 130. Since the outputs are inverted the CTL0 line is then forced low and the CTL1 line goes to high impedance.

The STIx lines are read by reading Peripheral Status (status register 5). The STIx lines have low-true polarity (1 = low). This polarity is not selectable.

### **Check STIx Status Example**

| 10 | Gpio=12                      | ! 12 = Interface Select Code |

|----|------------------------------|------------------------------|

| 20 | STATUS Gpio,5;Stat5          | ! Read Peripheral Status     |

| 30 | <pre>Sti0=BIT(Stat5,0)</pre> | ! Check the STIx bits        |

| 40 | <pre>Sti1=BIT(Stat5,1)</pre> |                              |

# **Using PSTS**

The PSTS line is generally used to indicate if peripheral communication is operational. The interface can be enabled to check it before every OUTPUT, ENTER and TRANSFER command by setting the PSTS Error bit of the Peripheral Control Register. Its status can be read at any time, whether or not PSTS Checking is enabled, by reading the PSTS OK bit of Peripheral Status.

If the PSTS input is left floating (not connected to anything), it will read a high. Therefore it is recommended to set the polarity to low = OK. This way a disconnected cable will return a PSTS not OK signal.

### Activate PSTS Checking Example

| 10 | Gpio=12                     | ! 12 = Interface Select Code |

|----|-----------------------------|------------------------------|

| 20 | Pcontrol=BINIOR(Pcontrol,4) | ! Set PSTS Check             |

### **Deactivate PSTS Checking Example**

| 10 | Gpio=12                                                  |

|----|----------------------------------------------------------|

| 15 | ! Clear a bit by ANDing the register with the compliment |

| 20 | Pcontrol=BINAND(Pcontrol,BINCMP(4)) ! Clear CTL1         |

| 30 | CONTROL Gpio,2;Pcontrol ! Write out value                |

|    |                                                          |

### **Read PSTS Value Example**

10 0 10

| 10 | Gpio=12               |   |                        |

|----|-----------------------|---|------------------------|

| 20 | STATUS Gpio,5;Pstatus | ! | Read Peripheral Status |

| 30 | Psts=BIT(Pstatus,2)   | ! | Check Psts bit         |

# **HTBasic GPIO Interrupts**

The GPIO interface supports Ready interrupts and External Interrupt Request (EIR) interrupts. Both of these interrupts are level-sensitive, this means that the signal must remain until it can be serviced. The service routine must be able to distinguish between the interrupts as they both call the same interrupt service routine.

### **Enabling Interrupts**

After LOAD BIN or reset the interrupts are disabled. They are enabled by writing a new mask into the Interrupt Enable Register. The mask identifies which interrupts will be allowed to cause an interrupt. Set each desired interrupt bit to enable it.

### Interrupt Mask Example

| 10 | Gpio=12                | ! 12 = Interface Select Code |

|----|------------------------|------------------------------|

| 20 | ON INTR Gpio GOSUB Int |                              |

| 30 | ENABLE INTR Gpio;1     | ! Set the mask to 1 for EIR  |

### **Interface Ready**

When the interface ready bit is set an interrupt occurs whenever the interface becomes ready. In Full-Mode Handshake the interface is ready whenever PCTL is clear and PFLG is ready. In Pulse-Mode Handshake the interface is ready when PCTL is clear regardless of the state of PFLG.

### **External Interrupt Request**

When the EIR bit is set an interrupt occurs whenever the EIR line goes low. The polarity of this line cannot be changed. This line must be kept low until it is inside the service routine or it may be missed by the program.

### **Interrupt Service Routine**

The interrupt service routine is the code that the computer executes if an interrupt occurs. A typical application is using an EIR interrupt to signal the computer that it has data available to be read. Interrupts are disabled after every call to the interrupt service routine. If the application requires multiple interrupts, the interrupts must be re-enabled during the interrupt service routine.

If both EIR and Interface Ready interrupts are enabled the service routine needs to be able to identify what caused the interrupt. This is accomplished by reading Interface Ready (status register 4) to see if the interface is ready or the EIR Line Low bit of Peripheral Status (status register 5) to check for an EIR interrupt.

The following example sets up an interrupt handler called <code>Gpio\_int</code> to read one character each time EIR goes low. Eleven integer values will be read and then stored in the <code>Samples</code> array. In this example the peripheral needs to clear EIR when the sample point is read.

### **Interrupt Controlled Input**

```

10

Gpio=12

20

Num samples=10

30

Count=0

40

INTEGER Samples(10)

50

ON INTR Gpio GOSUB Gpio int

60

ENABLE INTR Gpio;1

! Enable the EIR interrupt

70

! The loop below can be replace by useful code while waiting

80

! for the transfer to be completed

Loop: DISP TIME$ (TIMEDATE)

90

100

IF Count<Num samples THEN GOTO Loop ! Wait for transfer

DISP "Transfer is complete"

110

120

STOP

! This is the interrupt handling routine

200

Gpio int:

STATUS Gpio,5;Stat5

210

220

IF BIT(Stat5,2) THEN

! Check if a valid gpio interrupt exists

ENTER Gpio USING "W, #"; Samples (Count)

240

250

Count=Count+1

260

ENABLE INTR Gpio

! Peripheral needs to clear EIR before

! this statement

265

270

END IF

280

RETURN

290

END

```

# **READIO and WRITEIO Registers**

This section describes the GPIO Interface's READIO and WRITEIO registers. These registers are made to be as compatible as possible with the registers from the HP GPIO 98622A. They are not the physical registers that exist on either of the the GPIO boards. To use these registers the driver must be loaded. The actual physical registers are listed in the Programming Guide chapters of this manual.

In some cases both the HP and TransEra boards have similar bits but operation is different particularly with DMA operation. In these cases the control bits are left out of the READIO and WRITEIO registers.

READIO and WRITEIO registers should generally not be used. Most functions are available from STATUS and CONTROL register. Accessing WRITEIO registers can have undesirable effects by overriding settings that the software driver had set.

## **GPIO WRITEIO Registers**

WRITEIO Register 0-Set PCTL WRITEIO Register 1–Reset Interface WRITEIO Register 2–Interrupt Mask WRITEIO Register 3-Interrupt and DMA Enable WRITEIO Register 4–MSB of Data Out WRITEIO Register 5–LSB of Data Out WRITEIO Register 6–Undefined WRITEIO Register 7-Set Control Output Lines

## Set PCTL

## **WRITEIO Register 0**

Writing any non-zero numeric value to this register places PCTL in the Set state; writing zero causes no action.

DO10

D09

D08

#### **Reset Interface**

#### **WRITEIO Register 1**

Writing any non-zero numeric value to this register resets the interface.

#### **Interrupt Mask**

DO15

DO14

DO13

D012

#### **WRITEIO Register 2**

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 Value=12 Value = 64 Value = 32 Value = 16 Value = 8 Value = 4 Value = 2 Value = 1 8 0 Enable Enable Interface EIR Ready Interrupts Interrupts **Interrupt and DMA Enable WRITEIO Register 3** Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 Value=12 Value = 64 Value = 32 Value = 16 Value = 8 Value = 4 Value = 2 Value = 1 8 0 Enable Interrupt S **MSB of Data Out WRITEIO Register 4** Bit 7 Bit 4 Bit 2 Bit 6 Bit 5 Bit 3 Bit 1 Bit 0 Value=12 Value = 64 Value = 32 Value = 16 Value = 8 Value = 4 Value = 2 Value = 1 8 D011

## LSB of Data Out

#### **WRITEIO Register 5**

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 Value=12 Value = 64 Value = 32 Value = 16 Value = 8 Value = 4 Value = 2 Value = 1 8 D07 D06 D05 DO4 DO3 DO2 D01 D00

## **Set Control Output Lines**

#### **WRITEIO Register 7**

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Value=12

Value = 64

Value = 32

Value = 16

Value = 8

Value = 4

Value = 2

Value = 1

8

Value = 8

Value = 4

Value = 2

Value = 1

| 0 | Set CTL1<br>(1= Low;<br>0= High) | (1 = Low; |

|---|----------------------------------|-----------|

|   | 0 = mgm,                         | 0= mgn)   |

#### **GPIO READIO Registers**

Register 0-Interface Ready Register 1-Card Identification Register 2-Reserved Register 3-Interrupt Status Register 4-MSB of Data In Register 5-LSB of Data In Register 6-Reserved Register 7-Peripheral Status

#### **Interface Ready**

#### **READIO Register 0**

A 1 indicates that the interface is Ready for subsequent data transfers, and 0 indicates Not Ready.

#### **Board ID register**

#### **READIO Register 1**

This register always contains 3, the identification for GPIO interfaces.

#### **Interrupt Status**

#### **READIO Register 3**

| Bit 7      | Bit 6        | Bit 5      | Bit 4      | Bit 3     | Bit 2     | Bit 1     | Bit 0     |

|------------|--------------|------------|------------|-----------|-----------|-----------|-----------|

| Value=12   | Value = 64   | Value = 32 | Value = 16 | Value = 8 | Value = 4 | Value = 2 | Value = 1 |